# Interpretation of MOS transistor mismatch signature through statistical device simulations

Pietro Andricciola

# INTERPRETATION OF MOS TRANSISTOR MISMATCH SIGNATURE THROUGH STATISTICAL DEVICE SIMULATIONS

Pietro Andricciola

# INTERPRETATION OF MOS TRANSISTOR MISMATCH SIGNATURE THROUGH STATISTICAL DEVICE SIMULATIONS

### DISSERTATION

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof.dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday the 21<sup>st</sup> of December 2011 at 16:45

by

Pietro Andricciola born on the  $24^{\rm th}$  April 1982, in Venafro, Italy.

This dissertation is approved by the supervisor: prof.dr. Jurriaan Schmitz

Composition of the graduation committee:

Chairman: prof.dr.ir. A.J. Mouthaan Univ. of Twente, EWI Secretary: prof.dr.ir. A.J. Mouthaan Univ. of Twente, EWI Univ. of Twente, EWI Univ. of Twente, EWI Univ. of Twente, EWI Referees: dr.ir. H.P. Tuinhout NXP Semiconductors NXP Semiconductors

Members: prof.dr.ir. B. Nauta Univ. of Twente, EWI prof.dr.ir. R.A.M. Wolters Univ. of Twente, EWI

prof.dr. W. Krautschneider Hamburg Univ. of Technology

dr. E.T. Carlen Univ. of Twente, EWI

The research described in this thesis was carried out in the Device Modeling and Characterization group of NXP Semiconductors. The research was funded by the European Community through the Marie Curie project MOICCO.

Cover pictures made by Anita Tuinhout.

Published and distributed by: Ipskamp Drukkers, Enschede, The Netherlands.

ISBN: 978-90-365-3289-1

DOI number: 10.3990/1.9789036532891

Keywords: Mismatch signature, device simulation, temperature, interface states, CMOS, LDMOS.

Copyright © 2011 by Pietro Andricciola

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

Printed in The Netherlands.

# Contents

| 1        | Intr | roduction                                          | 1  |

|----------|------|----------------------------------------------------|----|

|          | 1.1  | TCAD and mismatch                                  | 4  |

|          | 1.2  | Mismatch model                                     | 6  |

|          | 1.3  | Characterization and experiments                   | 7  |

|          | 1.4  | About this thesis                                  | 9  |

| <b>2</b> | SiS  | PET and analysis methodology                       | 11 |

|          | 2.1  | TCAD and SiSPET                                    | 11 |

|          | 2.2  | Sources of mismatch                                | 13 |

|          |      | 2.2.1 Random Dopant Fluctuations                   | 14 |

|          |      | 2.2.2 Random Interface state Fluctuation           | 18 |

|          |      | 2.2.3 Random Series Resistance                     | 19 |

|          | 2.3  | TCAD calibration                                   | 22 |

|          |      | 2.3.1 Experimental setup and calibration procedure | 25 |

|          |      | 2.3.2 Body effect                                  | 27 |

|          | 2.4  | Mismatch analysis methodology                      | 29 |

|          |      | 2.4.1 Parameter extraction                         | 32 |

|          |      | 2.4.2 Mismatch signature                           | 32 |

|          | 2.5  | Summary                                            | 34 |

| 3        | Inte | erface state fluctuations                          | 37 |

|          | 3.1  | Interface states and mismatch signature            | 37 |

|          | 3.2  | Simulation of interface state fluctuations         | 43 |

|          | 3.3  | Compact modeling of RIF                            | 47 |

|          | 3.4  | A discussion on the implementation of RIF          | 52 |

vi CONTENTS

|             | 3.5   | Fast pulsed I-V measurements                                   | 54<br>55 |

|-------------|-------|----------------------------------------------------------------|----------|

|             | 3.6   | 3.5.2 Results and discussion                                   | 58<br>63 |

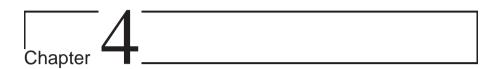

| 4           | Mis   | match in LDMOS Devices                                         | 65       |

|             | 4.1   | Introduction                                                   | 65       |

|             | 4.2   | Device description                                             | 66       |

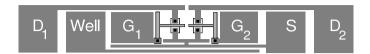

|             | 4.3   | Measurements                                                   | 66       |

|             |       | 4.3.1 Experimental methodology                                 | 66       |

|             |       | 4.3.2 Results                                                  | 68       |

|             | 4.4   | Simulations                                                    | 71       |

|             |       | 4.4.1 Influence of channel doping profile                      | 71       |

|             |       | 4.4.2 Other sources of mismatch                                | 73       |

|             |       | 4.4.3 Discussion                                               | 74       |

|             | 4.5   | Conclusion                                                     | 78       |

| 5           | Tom   | perature dependence of mismatch                                | 79       |

| J           | 5.1   | Introduction                                                   | 79       |

|             | 5.1   |                                                                | 82       |

|             | 5.2   | 5.1.1 Measurement methodology                                  | 83       |

|             | 5.3   | Subthreshold mismatch                                          | 84       |

|             | 5.4   |                                                                | 87       |

|             | 5.4   | Mismatch parameters                                            | 89       |

|             |       | 5.4.1 Threshold voltage mismatch                               | 90       |

|             |       | orna carreno menanacaren en e |          |

|             | F F   | 5.4.3 $I_{\text{ON}}$ mismatch                                 | 91       |

|             | 5.5   | Individual pair mismatch                                       | 92       |

|             | 5.6   | Conclusion                                                     | 99       |

| 6           |       |                                                                | 101      |

|             | 6.1   | Future work                                                    | 103      |

| Bi          | bliog | graphy                                                         | 104      |

| Sa          | men   | vatting                                                        | 117      |

| <b>C.</b> . | mms   | awy.                                                           | 121      |

| ъu          | mma   | ai y                                                           | 141      |

| Al          | out   | the author                                                     | 125      |

| Ac          | knov  | vledgment                                                      | 129      |

# List of Figures

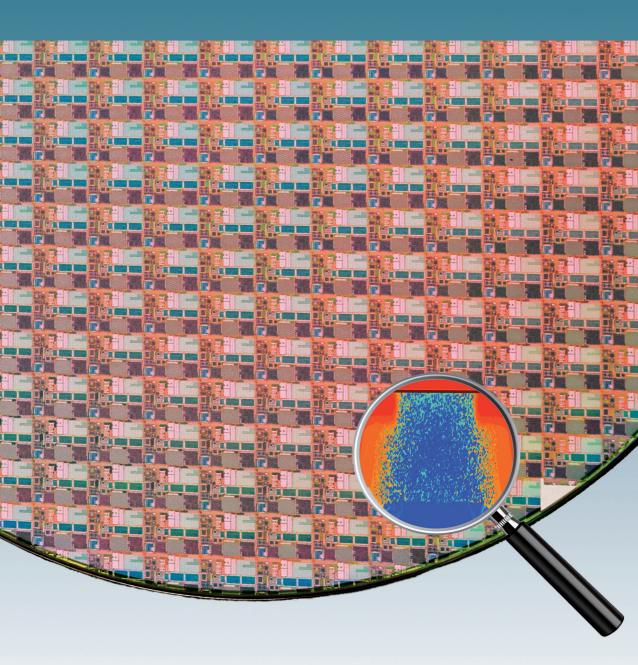

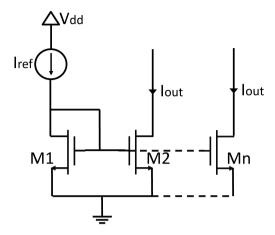

| 1.1  | Schematic representation of a current mirror                                                             | 3        |

|------|----------------------------------------------------------------------------------------------------------|----------|

| 2.1  | Screen shot of a part of a WorkBench project including the randomizer dr                                 | 13       |

| 2.2  | Illustration of the area calculation for a generic vertex                                                | 15       |

| 2.3  | Cross-section of a MOSFET after applying the randomization using 1 $\mu$ m as virtual depth              | 16       |

| 2.4  | Doping concentration for two randomized resistors with two different widths                              | 16       |

| 2.5  | Median currents resulting from a simulation of 51 randomized resistors applying different virtual width  | 17       |

| 2.6  | Terminology for charges in thermally oxidized silicon                                                    | 18       |

| 2.7  | Schematic representation of a cross-section of a MOSFET and the implementation of interface states in it | 19       |

| 2.8  | Schematic representation of the device structure including the external series resistances               | 20       |

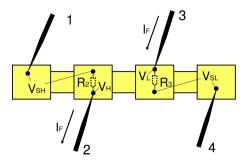

| 2.9  | Schematic of the test structure for probe-to-pad resistance measurements                                 | 21       |

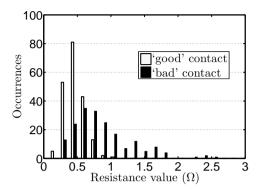

| 2.10 | Distribution of probe-to-pad resistances measured on 180 different positions                             | 22       |

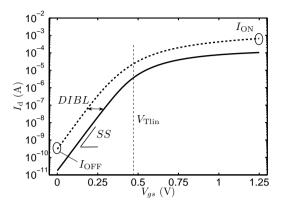

| 2.11 | Representation of the indicators used for the TCAD calibration                                           | 23       |

| 2.12 | on the two drain current curves                                                                          | 25<br>26 |

|      |                                                                                                          |          |

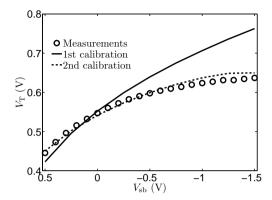

| 2.13 | Threshold voltage versus body bias for measurements and simulations                                                                               | 27 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

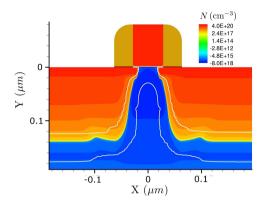

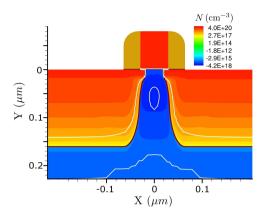

| 2.14 | Cross-section of simulated device with substrate bias of -1.5V and gate bias of 1.2V, first calibration                                           | 28 |

| 2.15 | Cross-section of simulated device with substrate bias of -1.5V and gate bias of 1.2V, second calibration                                          | 29 |

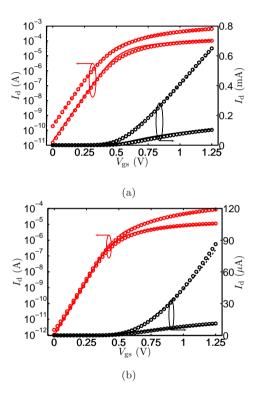

| 2.16 | Median drain currents of measurements and simulations after<br>the second calibration                                                             | 30 |

| 2.17 | Top-view of the pad-based test structure used for MOSFET mismatch characterization                                                                | 31 |

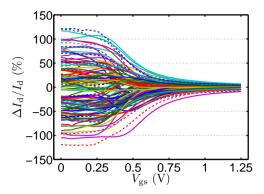

| 2.18 | "Mismatch sweeps": the relative drain current mismatch of individual matched pairs versus gate bias                                               | 33 |

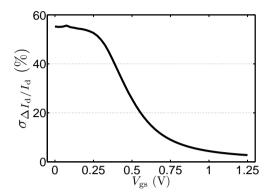

| 2.19 | "Fluctuation sweep": the standard deviation of the relative drain current mismatch of the whole population versus the applied gate-source voltage | 34 |

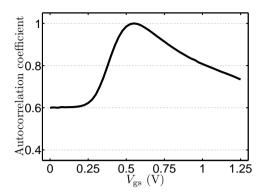

| 2.20 | "Autocorrelation plot": the autocorrelation coefficient between<br>the relative drain current mismatch at any gate bias and the                   |    |

|      | mismatch at $V_{\rm gs} = V_{\rm T}$ of the whole population                                                                                      | 35 |

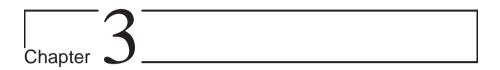

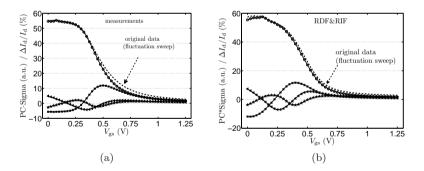

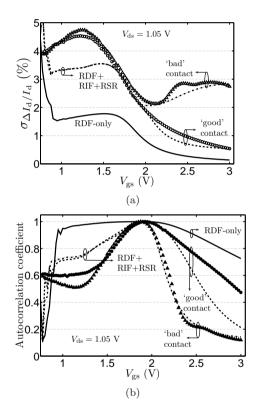

| 3.1  | An example of measured mismatch sweeps of 1/0.06 $\mu$ m/ $\mu$ m NMOS matched pairs                                                              | 38 |

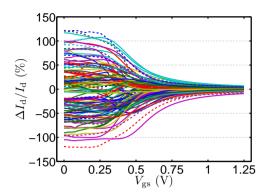

| 3.2  | Mismatch sweeps of 10/0.06 $\mu$ m/ $\mu$ m 51 NMOS transistors as obtained using RDF-only simulations                                            | 40 |

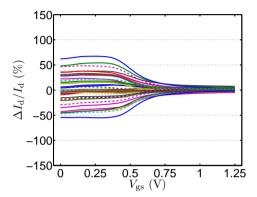

| 3.3  | Fluctuation sweeps of measurements and RDF simulations of $1/0.06~\mu\text{m}/\mu\text{m}$ NMOS transistors fabricated in C65 technology.         | 40 |

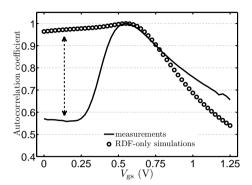

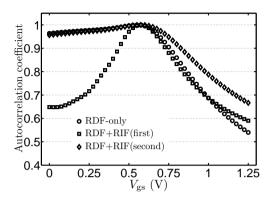

| 3.4  | Autocorrelation plots of measurements and RDF simulations of $1/0.06~\mu\text{m}/\mu\text{m}$ NMOS transistors fabricated in C65 technology.      | 41 |

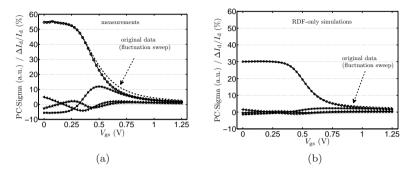

| 3.5  | Principal component analysis performed on mismatch sweeps obtained from measurements and RDF-only simulations                                     | 42 |

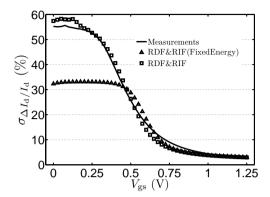

| 3.6  | Fluctuation sweeps of measured and simulated 60-nm devices                                                                                        | 44 |

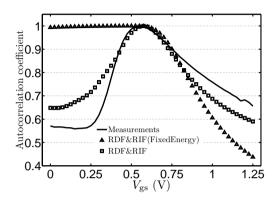

| 3.7  | Autocorrelation plots of measured and simulated 60-nm devices.                                                                                    | 45 |

| 3.8  | Principal component analysis performed on mismatch sweeps obtained from measurements and RDF& RIF simulations                                     | 45 |

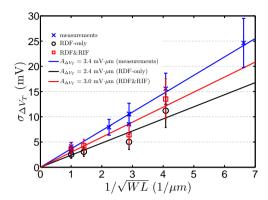

| 3.9  | Pelgrom's plot of threshold voltage mismatch                                                                                                      | 46 |

| 3.10 | Fluctuation sweeps obtained by using only one parameter of PSP                                                                                    |    |

|      | at the time                                                                                                                                       | 48 |

|      | Autocorrelation plots obtained by using only one parameter of PSP at the time                                                                     | 48 |

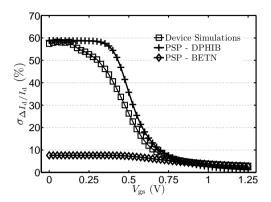

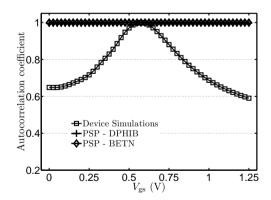

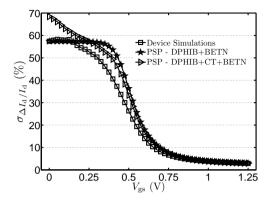

| 3.12 | Fluctuation sweeps obtained with the two approaches within PSP framework compared to the original simulated data.                                 | 49 |

| 3.13 | Autocorrelation plots obtained with the two approaches within PSP framework compared to the original simulated data | 50  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

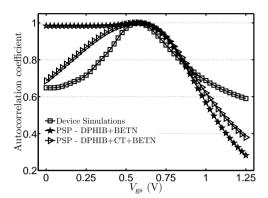

| 3.14 | Mismatch sweeps of original simulated data, drain currents ob-                                                      |     |

|      | tained with PSP with two-parameter and three-parameter sets.                                                        | 51  |

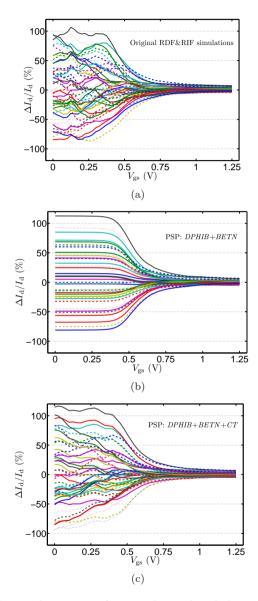

| 3.15 | Simplified flowchart of the new implementation of interface state                                                   |     |

|      | fluctuations in SiSPET                                                                                              | 52  |

| 3.16 | Comparison of fluctuation sweeps obtained with simulations of                                                       |     |

|      | RDF-only and with the two implementations of RIF                                                                    | 53  |

| 3.17 | Comparison of autocorrelation plots obtained with simulations                                                       |     |

|      | of RDF-only and with the two implementations of RIF                                                                 | 54  |

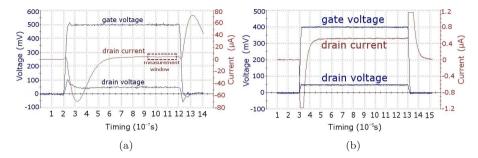

| 3.18 | Pulse waveforms measured with the PMU as visualized on the                                                          |     |

|      | 4200-SCS                                                                                                            | 56  |

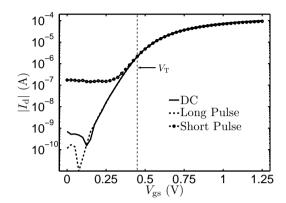

| 3.19 | Drain currents measured with the PMU with two different pulse                                                       |     |

|      | widths and a standard DC measurement                                                                                | 57  |

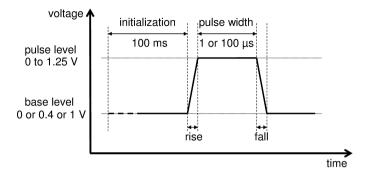

|      | Schematic representation of the pulse variables                                                                     | 58  |

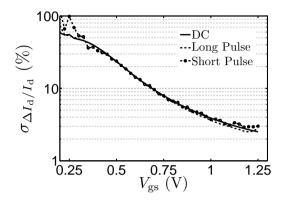

| 3.21 | Comparison between fluctuation sweeps of standard DC mea-                                                           |     |

|      | surements and pulse measurements both with base level of 0 V $$                                                     |     |

|      | but different pulse widths                                                                                          | 59  |

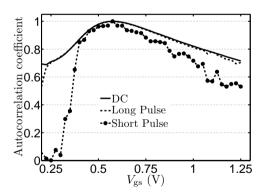

| 3.22 | Comparison between autocorrelation plots of standard DC mea-                                                        |     |

|      | surements and pulse measurements both with base level of 0 V                                                        |     |

|      | but different pulse widths                                                                                          | 59  |

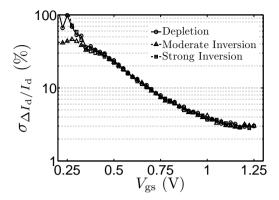

| 3.23 | Comparison between fluctuation sweeps of pulse measurements                                                         | 0.1 |

| 0.04 | all with the shortest pulse but with different base levels                                                          | 61  |

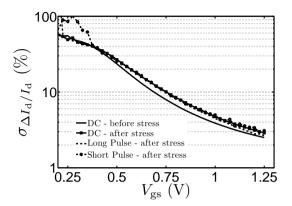

| 3.24 | Comparison between fluctuation sweeps of DC and pulse mea-                                                          | co  |

| 2.05 | surements performed on stressed devices                                                                             | 62  |

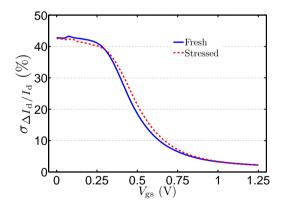

| 3.25 | Comparison between fluctuation sweeps obtained on fresh and                                                         | e o |

| 2 26 | HCI stressed device (DC measurements)                                                                               | 62  |

| 3.20 | HCI stressed device (DC measurements)                                                                               | 63  |

|      | itor stressed device (Do measurements)                                                                              | 00  |

| 4.1  | Schematic cross section of the simulated LDMOS transistor                                                           | 67  |

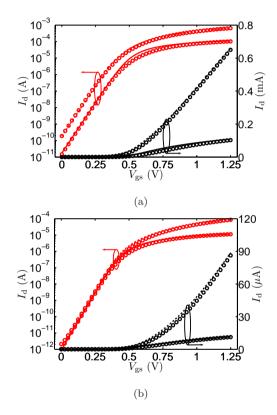

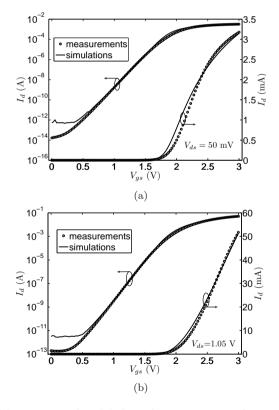

| 4.2  | Calibration results on LDMOS device                                                                                 | 67  |

| 4.3  | Mismatch signature of the two populations of LDMOSs                                                                 | 69  |

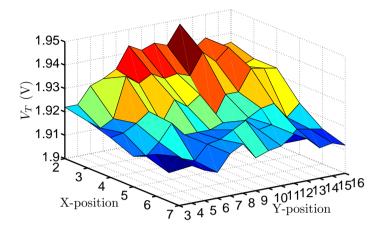

| 4.4  | Threshold voltage gradient across the wafer                                                                         | 70  |

| 4.5  | Representation of the three doping profiles used in RDF-only                                                        |     |

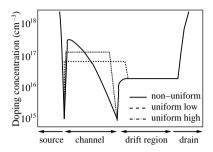

|      | simulations                                                                                                         | 71  |

| 4.6  | Comparison between the fluctuation sweeps of measured devices                                                       |     |

|      | and RDF-only simulations                                                                                            | 72  |

| 4.7  | Fluctuation sweeps for simulations (individual sources of mis-                                                      |     |

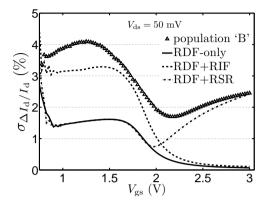

|      | match) and measurements                                                                                             | 75  |

| 4.8  | Fluctuation sweeps and autocorrelation plot for simulations (all sources of mismatch) and measurements at low drain bias                                               | 76  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | Fluctuation sweeps and autocorrelation plot for simulations (all sources of mismatch) and measurements at high drain bias                                              | 77  |

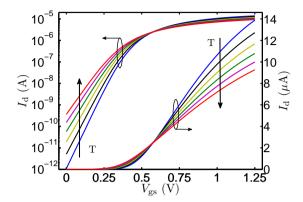

| 5.1  | Median values of drain current at different temperatures in logarithmic and linear scale for the shortest devices in C45                                               | 81  |

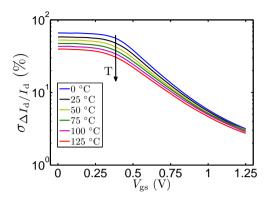

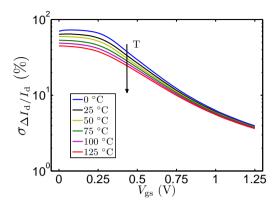

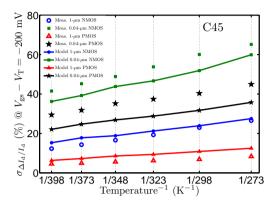

| 5.2  | Fluctuation sweeps of a population of shortest transistors in C45 (low drain bias)                                                                                     | 83  |

| 5.3  | Fluctuation sweeps of a population of shortest transistors in C45 (high drain bias)                                                                                    | 84  |

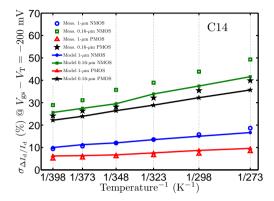

| 5.4  | Subthreshold mismatch for all the dimensions and types in C14.                                                                                                         | 85  |

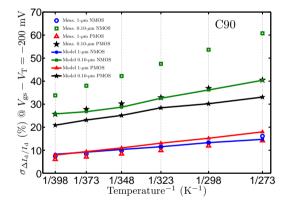

| 5.5  | Subthreshold mismatch for all the dimensions and types in C90.                                                                                                         | 85  |

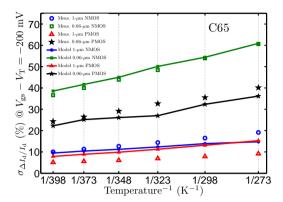

| 5.6  | Subthreshold mismatch for all the dimensions and types in C65.                                                                                                         | 86  |

| 5.7  | Subthreshold mismatch for all the dimensions and types in C45.                                                                                                         | 87  |

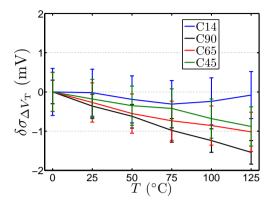

| 5.8  | Variation of threshold voltage mismatch with respect to the ones measured at 0 °C of PMOS with 1 $\mu m$ gate length for all four                                      | 0.0 |

| F 0  | technologies.                                                                                                                                                          | 89  |

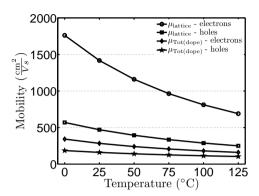

| 5.9  | Comparison of mobility values at different temperatures for elec-                                                                                                      | 00  |

| F 10 | trons and holes                                                                                                                                                        | 90  |

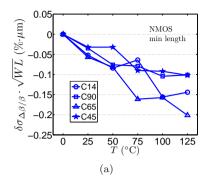

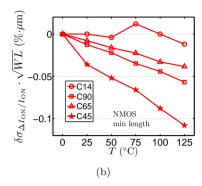

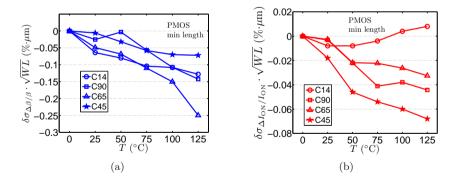

|      | Variation of $\sigma_{\Delta\beta/\beta}$ and $\sigma_{\Delta I_{\rm ON}/I_{\rm ON}}$ with respect to the ones measured at 0 °C for all four technologies (short NMOS) | 92  |

|      | Variation of $\sigma_{\Delta\beta/\beta}$ and $\sigma_{\Delta I_{\rm ON}/I_{\rm ON}}$ with respect to the ones measured at 0 °C for all four technologies (long NMOS)  | 93  |

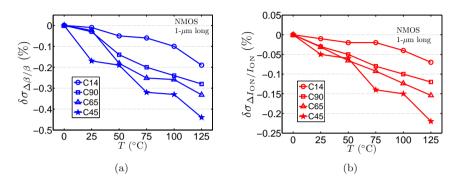

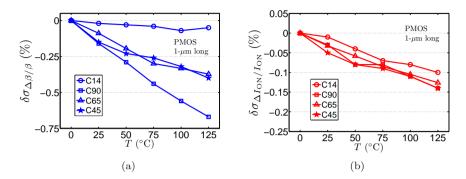

|      | Variation of $\sigma_{\Delta\beta/\beta}$ and $\sigma_{\Delta I_{\rm ON}/I_{\rm ON}}$ with respect to the ones measured at 0 °C for all four technologies (short PMOS) | 93  |

| 5.13 | Variation of $\sigma_{\Delta\beta/\beta}$ and $\sigma_{\Delta I_{\rm ON}/I_{\rm ON}}$ with respect to the ones measured at 0 °C for all four technologies (long PMOS)  | 94  |

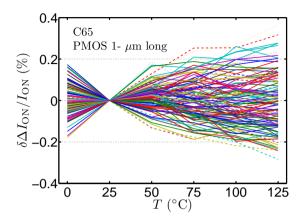

| 5.14 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus temperature (long PMOS)                                                                     | 95  |

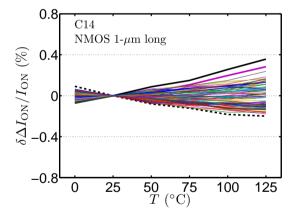

| 5.15 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus temperature (long NMOS C14)                                                                 | 95  |

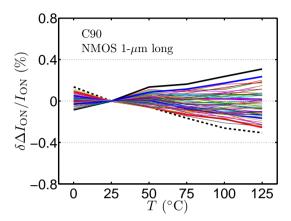

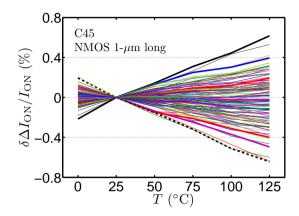

| 5.16 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus temperature (long NMOS C90)                                                                 | 96  |

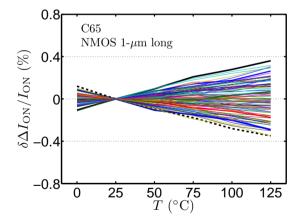

| 5.17 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus temperature (long NMOS C65)                                                                 | 96  |

| 5.18 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus temperature (long NMOS C45)                                                                 | 97  |

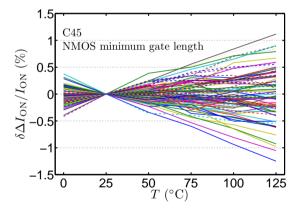

| 5.19 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus temperature (short NMOS C45)                                                                | 97  |

|      |                                                                                                                                                                        |     |

| T | IST | OE | TOTA         | CI | TD | TOC |

|---|-----|----|--------------|----|----|-----|

| L | TOT | Or | $\mathbf{r}$ | Gι | ın | E O |

| v | 1 |

|---|---|

| 5.20 | Drift of $\Delta I_{\rm ON}/I_{\rm ON}$ of individual matched pairs versus tempera- |    |

|------|-------------------------------------------------------------------------------------|----|

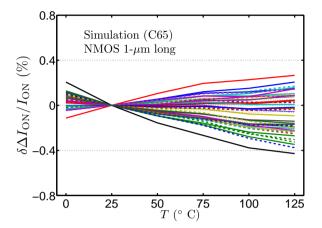

|      | ture (simulations)                                                                  | 98 |

|      |                                                                                     |    |

# List of Tables

| 5.1 | General information about the technologies under test      | 81 |

|-----|------------------------------------------------------------|----|

| 5.2 | Summary of the change of the mismatch parameters over tem- |    |

|     | perature and relative short term repeatability             | 88 |

|              | 1 |  |  |  |  |

|--------------|---|--|--|--|--|

| l<br>Chapter |   |  |  |  |  |

# Introduction

Semiconductor manufacturers daily fabricate millions of nominally identical integrated circuits made of supposedly identical components. However controlled the fabrication process can be, two components will always be slightly different when thoroughly compared. The comparison between two components is usually done using a certain parameter as estimator of the integrated circuit (IC) or transistor performance, e.g. a frequency of an oscillator or a current delivered by a transistor. What happens in reality is, for instance, that the frequencies of the identical oscillators fabricated, with the same process but in different foundries, or in different moments in the same foundry, will be different. Actually, even chips fabricated on the same wafer will not be exactly the same, as some fundamental characteristics of the fabrication process vary across the wafer. These sorts of variability are often deterministic. This means that a clear pattern appears after a significant number of observations.

Let us consider the following example where the resistance value of a resistor varies wafer after wafer. The median value of this resistance for wafer 1 is 51  $\Omega$  while for wafer 2 is 52  $\Omega$  and so on, with the resistance that slightly increases wafer after wafer. This could be an indication of a change (gas flow, temperature, pressure) that is happening in one of the machines used to fabricate these resistors. With a proper monitoring and feedback this trend can be compensated.

The same applies to parametric gradients across a wafer. If the differences among the values of the resistor are consistent with the position on the wafer it means that some process parameters are position dependent inside the machine and the technologist can tune the machine to reduce the variation to the

minimum. The process will be released for designing electronic circuit with a nominal value per parameter and a certain window around it. The circuit and layout implementation final design must assure that the chip will work for any value of that parameter, given that it is within the process window provided.

Last but not least, there is the variability on the smallest length scale that includes the differences between supposedly identical components within the same chip. This is typically indicated with the term **mismatch** or **matching**. Differently from the other types of variability mentioned above, mismatch is usually random; it can therefore not be adjusted and compensated during the fabrication. Random mismatch is generally attributed to microscopic device architecture fluctuations, e.g. the fluctuation of the position and the number of dopants in a transistor (controlled by stochastic processes) [1]. A key element of the discussions about matching, or variability associated with microscopic stochastic fluctuations, is that the equality between supposedly identical components becomes better when the devices are made larger (the fluctuations average out) [2].

Although the mismatch represents only a part of the total variability that can be measured on multiple wafers, it is, in many cases, a performance limiter. For a correct functionality of an integrated circuit (IC), identically designed components fabricated on the same circuit need to have the same performance. As a matter of fact, complex circuits base their functionality on simpler, but fundamental, circuit blocks. Many of such blocks, e.g., bandgap references, current mirrors, differential amplifiers etc., rely on the availability of multiple identical active and passive components. But as already argued, two allegedly identical components will never be exactly the same.

The following example of a current mirror demonstrates how mismatch affects the function of a simple block. In figure 1.1 a schematic representation of such circuit is drawn. The purpose of this circuit is to replicate the reference current ( $I_{\rm ref}$ ) in order to supply it to other parts of the IC. The reference current is usually obtained through a complicate circuitry that stabilizes the current making it robust against supply voltage and temperature variations. The n devices represented in figure 1.1, M1, M2 and so on to Mn, have the gate and source terminals connected together. This means that if M2 (or Mn) and M1 are nominally identical, the current that will flow in M2 (Mn),  $I_{\rm out}$ , should be an exact replica as the current that is forced into M1,  $I_{\rm ref}$ . In reality  $I_{\rm out}$  and  $I_{\rm ref}$  will always be different, as M2 (Mn) and M1 will always be microscopically different.

Using a simple three-stage circuit for signal processing, it has been shown that the mismatch is the limiting factor for the overall performance of the whole circuit [3]. The performance of such a circuit is judged by looking at its ac-

Figure 1.1: Schematic representation of a current mirror. This fundamental block is needed to replicate a reference current and bring it to other parts of the chip.

curacy, speed and power consumption. The accuracy is strongly dependent on the mismatch and improves with larger transistors. Apart from the additional cost that larger transistors would bring along, also the other two performance indicators will suffer from the choice of big transistors. In case of CMOS, a wider transistor results in higher current, thus increasing the speed but also power consumption, while a longer transistor reduces the current, thus the power, but increases its capacitance slowing down the chip. The design choice will be a trade-off between these performance indicators and it is limited by the matching properties of the technology [3].

In the past, when electronic system design was dominated by vacuum tubes and discrete components, the realization of a circuit was done by handpicking transistors and passive elements and connecting them together. It was therefore possible to choose ('match'), from the same kind of components, the one that had the closest performance to the design specifications and be sure that the final result had a perfect matching. Of course, this cannot be done for an IC with the current process technology.

From the variability point of view, a working IC is a challenge that spans across at least three different levels. One is the process technology: the fabrication process should be such that its variability remains below manageable levels. Another one is the characterization and modeling of the mismatch properties, because only with good models and reliable estimators is possible

to make accurate predictions. Finally, the third area is the circuit design; the circuits need to be robust against the variations foreseen by the models. Without a combined effort in all these three fields, the fabrication of contemporary working IC would not be successful.

This thesis contributes predominantly to the second task: it aims at expanding the understanding and the characterization of mismatch of modern Metal Oxide Semiconductor (MOS) transistors. The investigation is done with device simulations and high-precision measurements. In the following sections the simulations, the characterization and the modeling of the MOS transistor mismatch are briefly summarized.

### 1.1 TCAD and mismatch

In the past decades, computer aided device and process simulations, generally called TCAD, have become very important tools of the semiconductor industry. The improvements in the accuracy of the device-physics description, the development of efficient multidimensional equation solvers and the increasing availability of 'low-cost' computational power transformed the use of TCAD simulations from mere support to an indispensable R&D tool, especially in early stage of technology development [4, 5]. TCAD is also used by modeling experts and device physicists to obtain better understanding of the physical behavior of the device and to investigate unforeseen behavior encountered in actual device measurements. TCAD simulations have been also used to confirm mismatch relations and investigate the impact of sources of fluctuations, especially Random Dopant Fluctuations (RDF). A clear example of how to use device simulations to confirm analytical model is given by the study of the impact of RDF on threshold voltage mismatch in MOS transistors carried out by Stolk et al. [6]. With a 2-D drift diffusion simulation they validated their model of the threshold voltage fluctuation in a uniformly doped transistor. Taking into account the fluctuations of the surface potential and the electric field they confirmed and refined the work of Pelgrom et al. [2]: the standard deviation of the threshold voltage fluctuation is inversely proportional to the square root of the active area and proportional to the fourth root of the doping concentration (see equation 4.1 in chapter 4 for the complete formulation).

Furthermore, in the last decades, device simulation has been extensively developed and improved to enable analysis of the random variability of device performance [7, 8, 9, 10, 11]. In that respect, many efforts, such as from the group of Device Modeling at Glasgow University, went into adding sources of variability to Drift-Diffusion (DD) as well as Monte Carlo (MC) based simula-

tors [12, 13].

DD simulations play the role of the work-horse in semiconductor R&D because of the very good trade-off between speed and accuracy. It proved possible to study the effect of RDF, Line Edge Roughness (LER), Poly-Grain Boundaries (PGB) and several other factors, in contemporary and future technology nodes [12, 14, 15]. For example, the contribution of RDF and LER was investigated in transistors of less than 20 nm of channel length, showing that both contributors would have a dramatic effect on the functionality of the device and the resulting circuits built with them. This represents a proof of the need for a different architecture of the transistor (a drive for 3-D transistor structure), alternative gate composition, and/or a more advanced lithography tool (a drive for Extreme Ultra Violet source).

In this thesis the approach is different. This research was carried out in the process technology laboratory of NXP Semiconductors [16]. During the years of this study, NXP did not focus its strategy on the development of future CMOS nodes and therefore on the analysis of the variability associated with those, but reinforced strong interests in high-performance mixed-signal circuits [17] largely based on NXP's Philips heritage in analog and mixed-signal product lines. This research led to a better understanding of the mismatch causes and dynamics in existing, production ready, technologies (somewhat larger devices). For this task, it proved crucial to have a tool that allows studying the impact of different sources of mismatch on transistor behavior and compare those with measurements and models. Developed in a collaboration between Uppsala University and Philips Research [18], the Simulated Statistical Parameter Extraction Tool (SiSPET) is the tool that has been used (and expanded) throughout this thesis to investigate MOS transistor mismatch. It consists of a 2-D DD device simulator, a randomizer used to insert sources of variability in the nominal virtual device and various scripts and several routines for data analysis and parameter extraction.

A tool like SiSPET is aimed at two main results. In the first place, short-comings in existing mismatch models can be identified, understood and perhaps overcome. This, in turn, will raise the confidence in models circuit designers can use for cutting edge solutions and will reduce both the number of necessary design spins for a fully-functional circuit, as well as the silicon area needed to fulfill the mismatch requirements. Second, a tool capable to deal with device variability represents a first-line help in cases of yield issues or unexpected behavior. If a circuit malfunction is attributable to random variations, a tool like SiSPET can confirm or reject the hypothesis in relatively short time without expensive silicon experiments. The merits and limitations of this tool are discussed in this thesis.

### 1.2 Mismatch model

Although mismatch becomes worse when device dimensions reduce, which means it is becoming every day more important, one of the first investigations of the impact of threshold voltage fluctuations on MOSFET technology was published already roughly 40 years ago, in 1972, by Hoeneisen and Mead [19].

The golden age of the literature about mismatch is probably the 80's. In fact, in 1984 the first model for MOS transistors that included a dimensional dependency was proposed by Shyu et al. [20]. That work was experimentally confirmed and expanded by Lakshmikumar et al. [21] in 1986. Three years after that, Pelgrom et al. [2] derived a general model, independent from the causes of mismatch, that mathematically describes the dimensional dependence of MOS transistor random mismatch (and it was found to hold also for all components that fall under their assumptions). This work resulted in the so-called "Pelgrom law" and it can be summarized as follows.

The differences between two electronic components are estimated through the measurement (or extracted via a model) of an electrical parameter P, e.g., resistance, current, voltage etc. If the dimensions of the underlying physical causes of these parametric changes are small with respect to the device dimensions, and mutually independent, the mismatch fluctuation standard deviation  $\sigma_{\Delta P}$  (or  $\sigma_{\Delta P/P}$  if the parameter variations should be considered in relative values) of an electrical parameter P scales with the inverse of the square root of the device area, in symbols:

$$\sigma_{\Delta P} = A_{\Delta P} / \sqrt{W \times L} \tag{1.1}$$

or

$$\sigma_{\Delta P/P} = A_{\Delta P/P} / \sqrt{W \times L} \tag{1.2}$$

where W and L are the effective dimensions of the active region of the device. The A-factor  $A_{\Delta P}$  (or  $A_{\Delta P/P}$ ), often referred to as Pelgrom-factor or area factor, is characteristic of a technology and in first approximation describes the mismatch properties of a parameter for a particular technology. One of the most remarkable observations about these microscopic parametric mismatch fluctuations is that, under the assumptions introduced by Pelgrom et al., the behavior described by the equation 1.1 is encountered for all integrated circuit device types and for most of their observables or parameters. This relatively simple equation can give an idea of what is the order of magnitude of contemporary mismatch. Let us assume that a technology has an area factor for

the threshold voltage mismatch of 3 mV $\mu$ m and the transistor dimensions are  $L=0.04~\mu{\rm m}$  and  $W=0.2~\mu{\rm m}$ . The resulting standard deviation of the relative drain current mismatch is  $\sigma_{\Delta V_{\rm T}}\approx 33$  mV. In large ICs, with millions of components, the calculation of the possible variation of the drain current for this technology needs to be done on four or five sigmas. In this case, the design should be robust against variations that can reach  $\pm$  150 mV, that is a substantial part of the supply voltage. This example explains why the scientific community, as well as the design and manufacturing communities, are dedicating much attention to the problem of mismatch.

Despite the usability of the model proposed by Pelgrom (which is limited by its fundamental assumptions), many other models have been published over the years. For example, Croon [22] and Drennan et al. [23], in different studies, focused their modeling efforts on drain current mismatch on the full bias range. Croon provided a physically-based drain current model that correctly described drain current mismatch by separating the contribution of the threshold voltage mismatch and the current factor mismatch. A broader approach was followed by Drennan which, with a technique called Back Propagation of Variance (BPV), linked the drain current mismatch to numerous independent process parameter variations. By doing so, he obtained a matrix of sensitivities of the drain current with respect to each of the process parameters of a particular technology node.

In recent years, the group of Takeuchi proposed a new geometry scaling model, different from Pelgrom's by adding some extra technology-related parameters which trends give an idea of the effect of different sources of mismatch among different technology nodes [24, 25].

## 1.3 Characterization and experiments

As it is in any science, actual experiments, measurements and analysis method need to be produced to prove theory and quantify effects. Mizuno et al. were one of the first to publish an experimental study on the threshold voltage fluctuation due to random dopant fluctuations based on large population of devices [26]. Several experiments have been performed over the years on the impact of certain process conditions on the mismatch. A good example of these experiments is the study of the impact of metal coverage, and gate depletion with boron penetration on MOS transistor mismatch, both published by Tuinhout et al. [27, 28]. Many other contributions about test structures and analysis methods appear regularly at the International Conference on Microelectronics Test Structure (ICMTS) [29]. Other examples of the kind of

contributions that help device scientist to better deal with the characterization of subtle mismatch effects are the comparison of five different methods of threshold voltage extraction (among which one was proven to be the best one, yet with many shortcomings) [30] and the analysis of an abnormally high electrical fluctuations in heavily pocket<sup>1</sup> implanted transistors [31].

Beside good test structure and well designed experiments, a good mismatch analysis needs to be free from misconceptions that can lead to wrong conclusions. An example of such misconceptions is the use of relative threshold mismatch,  $\Delta V_{\rm T}/V_{\rm T}$ , when comparing mismatch properties of populations with different nominal threshold voltages. For instance, the variation of the relative threshold voltage has been used for mismatch analysis in cases of threshold voltage change due to different temperatures or different body biases [32, 33]. This is incorrect for the following reasons. First, if the threshold voltage goes to zero, the relative quantity,  $\Delta V_{\rm T}/V_{\rm T}$ , yields an infinite mismatch, so this definition is not applicable to "normally on" and so-called native devices. Second, the approach with relative threshold voltage mismatch is misleading. As a matter of fact, an increase in the relative threshold voltage mismatch results in a reduction of the drain current mismatch. For example, for  $V_{\rm ds} \gg (V_{\rm gs} - V_{\rm T})$ , the drain current (in saturation) can be expressed in its simplest form by:

$$I_{\rm d} = \frac{\beta}{2} (V_{\rm gs} - V_{\rm T})^2 \tag{1.3}$$

where  $\beta$  is the current factor. This leads to an expression of the variance of the relative drain current mismatch that reads:

$$(\sigma_{\Delta I_{\rm d}/I_{\rm d}})^2 = \frac{4(\sigma_{\Delta V_{\rm T}})^2}{(V_{\rm gs} - V_{\rm T})^2} + (\sigma_{\Delta \beta/\beta})^2$$

(1.4)

with obvious meaning of all the symbols. The first term of the right-hand side of equation (1.4) is proportional to the variance of absolute threshold voltage mismatch and inversely proportional to the square of the gate overdrive  $V_{\rm gs}-V_{\rm T}$ . Thus, for the same gate bias and same absolute threshold voltage mismatch, when the threshold voltage reduces the overdrive increases, consequently diminishing the contribution of the threshold voltage mismatch to the overall drain current mismatch. The use of relative threshold voltage mismatch would give the exact opposite result: to a larger relative  $V_{\rm T}$  mismatch will correspond a smaller relative drain current mismatch. This is rather counterintuitive.

Given these considerations, the threshold voltage mismatch should be always reported and analyzed in its absolute-value form. This example does

<sup>&</sup>lt;sup>1</sup>The pockets are doping implants with a high angle of implantation used to overcome short channel effects in contemporary CMOS devices.

demonstrate how even with a very advanced simulation or a fully thought through experiment wrong results can easily be obtained if no proper analysis methods are used.

## 1.4 About this thesis

This thesis is the result of a Twente University PhD project carried out in the Device Modeling and Characterization group of NXP Semiconductors in Eindhoven. This project has been sponsored by the European Community through the Marie Curie Action MOICCO. The fact that the project was positioned between industry and university (as PhD program) led to a good balance between simulations and characterization work with an eye always directed to modeling and possible applications.

The study of internal and external factors influencing MOS transistor mismatch was born following the necessity of contributing something new to this field and of helping, at the same time, NXP designers with concrete feedback on how to obtain better products. It was therefore decided to focus on existing technology nodes already available in production, e.g., 65 nm minimum gate length, and on developing a software suite and a simple analysis methodology that would help in identifying possible mismatch problems and in distinguishing the different causes of mismatch.

These general directions converged into the study of:

- the impact of random dopant fluctuations and interface state fluctuations on MOS transistor mismatch, with the help of our simulation tool and an advanced measurement equipment;

- the impact of channel doping non-uniformity, interface state fluctuations and series resistance fluctuations on LDMOS transistor mismatch with our simulation tool trying to reproduce measurement results;

- the impact of temperature on MOS transistor mismatch across four technology nodes mainly with measurements and confirmed a theoretical explanation with simulations.

This thesis is thus structured as follows: first the simulation approach and the analysis methodology are explained in chapter 2.

The impact of interface state fluctuations on MOS transistor mismatch is investigated in the subsequent chapter. In that chapter the simulator is used to prove a measured device behavior believed to be caused by interface state fluctuations. Some elementary modeling work and very fast I-V pulsed

measurement have been performed and their results are discussed in the same chapter.

An application of our methodology to study LDMOS mismatch properties is discussed in chapter 4.

The temperature effect on MOS transistor mismatch across four different technology nodes is presented in chapter 5.

Finally, in chapter 6 the main conclusions are summarized.

# SiSPET and analysis methodology

This chapter is about the software and tools used during this research activity. It starts by outlining the essential characteristics of our main tool: SiSPET (Simulated Statistical Parameter Extraction Tool). Then, the implementation of the different sources of fluctuation that are built into the tool is explained. In the next section "TCAD calibration", the procedure to obtain a good simulated replica of an actual transistor is discussed. Finally, the data analysis methodology used throughout this thesis is described.

## 2.1 TCAD and SiSPET

SiSPET is a tool for the evaluation of the influence of mismatch sources on the device behavior and also on compact models. It was developed in a collaboration between Uppsala University and Philips Research [18]. SiSPET consists of a suite of commercially available programs for device simulation (Synopsys) and data analysis (mostly Matlab [34]), a model parameter extraction tool (implemented through ICCAP [35]) and a microscopic device architecture randomizer (dr). Although some solutions to introduce sources of fluctuation, usually RDF, are already implemented at a higher level as noise disturbances in some simulators, e.g. Sentaurus Device (SD) [36], a true device randomizer was developed in-house and used for the study. This provides a higher flexibility and better control, and the possibility to trace back and exactly reproduce any

randomized device. The simulation framework of SiSPET is described here, leaving the analysis methodology for the end of this chapter while the model parameter extraction is discussed in detail in chapter 3.

The analyzed devices were not generated through process simulations, but were created using the Sentaurus Structure Editor (SSE) [37]: it allows the creation of any structure with different kinds of material and doping concentration. SSE is preferred over a process simulator because it is much faster and it provides a better controllability of the actual device construction (down to a single grid point). In any case, this study was not meant to investigate the influence of process steps on mismatch but to analyze device architecture and resulting fluctuations of electrical device properties.

For extensive statistical device simulation, the main characteristics that the simulator needs to have are speed, accuracy and availability of standard models. Although it is widely published that a Monte Carlo simulation approach yields the best accuracy, especially for very short transistors, the time needed to complete a simulation can be very long. Several attempts of using MC simulations for statistical variability have been reported [13], but those studies all analyze extremely small transistors. In this study, several, relatively large device sizes of a technology have been simulated. This was largely the results of the strategy of NXP, which mainly focused its product portfolio towards high-performance mixed-signal circuits. Since statistical simulations are needed, i.e., many simulation instances, a faster but "accurate enough" approach is preferable. Given these requirements, the devices (before and after randomization) were simulated with Sentaurus Device a commercial drift-diffusion device simulator from Synopsys [36] in its two-dimensional (2-D) version.

The device randomizer, basically the heart of SiSPET, is based on a series of scripts and programs written in **Ruby** [38], an open-source programming language. Although during the course of the research several modifications were made to the programs, especially to add new sources of variation initially not implemented, the basic structure remains the same as originally built [18]. The basic idea is that the randomizer manipulates the input files of the device simulator. One can therefore modify in a controlled manner any device characteristic, e.g. a doping concentration associated with a grid point or a resistance value in the electrode definition.

The procedure is basically as follows: first the unperturbed device is created and calibrated to assure realistic I-V curves, then the resulting data file, describing the device, is used as input to the randomizer after which multiple microscopically different devices are created and subsequently simulated. The user interface of the randomizer is inserted into the Sentaurus WorkBench (SWB) [39] that allows the feeding of variables and parameters to the various

|            | Family Tree |  |      |           |     |  |  |

|------------|-------------|--|------|-----------|-----|--|--|

| SankurusSi |             |  |      | ŞenaurusD |     |  |  |

|            | GateL       |  | SEED |           | Vg  |  |  |

|            |             |  | 1903 |           | 1.2 |  |  |

|            | 0.06        |  | 1904 |           | 1.2 |  |  |

|            |             |  | 1905 |           | 1.2 |  |  |

|            |             |  | 1906 |           | 1.2 |  |  |

|            |             |  | 1907 |           | 1.2 |  |  |

|            |             |  | 1908 |           | 1.2 |  |  |

|            |             |  | 1909 |           | 1.2 |  |  |

|            |             |  | 1910 |           | 1.2 |  |  |

|            |             |  | 1911 |           | 1.2 |  |  |

|            |             |  | 1912 |           | 1.2 |  |  |

|            |             |  | 1913 |           | 1.2 |  |  |

|            |             |  | 1914 |           | 1.2 |  |  |

|            |             |  | 1915 |           | 1.2 |  |  |

|            |             |  | 1916 |           | 1.2 |  |  |

Figure 2.1: Screen shot of a part of a WorkBench project including the randomizer dr.

programs through the user interface and a smooth interaction of user-defined programs and Synopsys elements. In figure 2.1 a screen shot of the WorkBench with a typical SiSPET project is shown. The gate length of the device (GateL variable in the SSE part on the left), the randomizer seed number (SEED in the  $d\mathbf{r}$  section in the middle) and the maximum gate voltage ( $V_{\rm g}$  for SD on the right) are the modifiable variables in this example.

The randomizer used in this tool is based upon a pseudo-random number generator [40] and the seed represents a key to generate a unique and repeatable sequence of pseudo-random numbers. Using the same seed, one can recreate the exact same sequence of random numbers as created the first time. This is an important feature to be able to trace back each perturbed device in relation to the created device architecture change. The sequence of pseudo-random numbers are used to add stochastic variations (dopant number, oxide traps etc.) to the 'nominal' device. The implementation of the specific sources of fluctuations investigated within this research project is described in the next section.

## 2.2 Sources of mismatch

Parametric mismatch fluctuations measured on dedicated test structures are generally the final result of a combination of multiple sources of fluctuation. In order to obtain a better understanding of the mismatch behavior of the device it is of fundamental importance to analyze the individual causes in detail. Statistical simulations represent an easy and fast way (in fact probably the only viable way) to study the effect of **controlled** mismatch causes in modern MOS

device architectures.

There are examples of very well controlled experiments (see [28] for an experiment of the impact of boron penetration on mismatch) but they are certainly very expensive and are not always successful. One may argue that the use of a compact model is a very fast and inexpensive way to see the effect of individual sources of mismatch as well. A compact model is an analytical model that, based on the physics of the device through compact equations, describes quite accurately the behavior of the device. The shortcoming of compact models, however, comes with the fact that often not all the quantities in the equations are linked to each other through actual physical relations. Also the approximations made to make the model "compact" might be such that subtle mismatch signatures will not be captured.

In particular, the main goal of research activities in this field should be aimed at identifying the most important sources of mismatch and verifying how these affect the device variability and interact with each other. The main cause of mismatch in MOS technologies is believed to be the random dopant fluctuations. For instance, it has been shown that RDF explain roughly 60 % of the total mismatch in a 65-nm technology node [41]. However, in order to create a complete description of the device behavior, other sources of mismatch are essential. As mentioned in chapter 1, LER and PGB are those that attracted the most attention [14, 15, 42]. For their importance in the weak inversion operation region of the device, Random Interface state Fluctuations (RIF) are proposed here in this thesis as one of the most important source of variability in MOSFET mismatch after RDF [43]. Furthermore, a third source, especially important when the device operates with elevated currents is discussed in this thesis: the Random Series Resistance fluctuations (RSR). In fact, it can mimic either an incidental metalization asymmetry or a fluctuating probe-to-pad contact resistance [44].

## 2.2.1 Random Dopant Fluctuations

The implementation of RDF in a drift-diffusion simulator presents a series of challenges and compromises, very well described (and mostly solved) by G. Roy in [45]. For this particular implementation some of those challenges had to be faced again to assess the capabilities and limitations of our own tool.

One basic assumption of the implementation of the doping randomization is that the positions of impurities on an atomic scale are not correlated, therefore the number of dopants in a given volume follows a stochastic Poisson distribution [1]. For simplicity, the volume and thus the assignment of the random dopants is strictly linked to the grid (mesh) generated by the Synopsys tool.

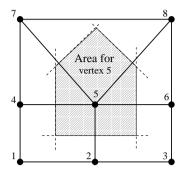

Figure 2.2: Illustration of the area calculation for a generic vertex. The numbers represent the labeling of the vertexes as done by Sentaurus. This area will be multiplied by a virtual width obtaining the volume associated with the grid point number 5.

The volume is calculated by multiplying the area that surrounds the grid point with a virtual width (depth), typically 1  $\mu$ m. The area is calculated applying the shoelace algorithm [46] to a polygon obtained with the interception of the mid-point perpendiculars of the edges which connect the grid point to the adjacent ones (see figure 2.2). The number of dopants in a volume is:

$$n = N \cdot Area \cdot z \tag{2.1}$$

where N is the concentration of impurity atoms, Area is the area associated to the grid point and z is the virtual depth of the device. The number n, thus obtained, is the nominal number that will be randomized following a Poisson distribution, yielding  $\tilde{n}$  and then reconverted in impurity concentration,  $\tilde{N}$ . This concentration is then reassigned to the original grid point. This results in an adapted version of the Nearest Grid Point method [47]. When the grid is very dense, especially close to the oxide interface, where a very fine mesh is required for a proper device simulation, it can happen that the nominal number of dopants in a given volume is less than one. In that case the Poisson random number generator will often return a zero as result. This is a situation that must be avoided. Drift-diffusion simulators, in particular their mobility models, rely on the fact that the doping does have realistic values, typically between  $1 \cdot 10^{14}$  cm<sup>-3</sup> and  $1 \cdot 10^{20}$  cm<sup>-3</sup>. Outside of this range the simulator might give unrealistic results.

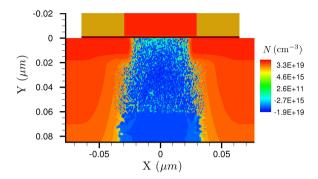

An example of a cross-section of a MOSFET after randomization using  $z=1~\mu\mathrm{m}$  is represented in figure 2.3. Many areas are visible with very low

Figure 2.3: Cross-section of a MOSFET after applying the randomization using 1  $\mu$ m as virtual depth. The upper part of the channel of the randomized device presents many 'zero' (green) areas.

Figure 2.4: Doping concentration for two randomized resistors with two different widths 1  $\mu$ m (a) and 10  $\mu$ m (b). Red areas in (a) correspond to zero doping.

doping corresponding to grid points that correspond to zero dopant after randomization (green regions).

### An example: a resistor

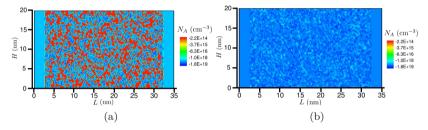

A simulation example of a simple resistor demonstrates quite well what happens in this unfavorable situation. Consider a piece of silicon of  $20 \text{ nm} \times 35 \text{ nm} \times 1 \mu \text{m}$  (H×L×W) p-type doped with boron at a concentration of  $5 \cdot 10^{18} \text{cm}^{-3}$ . The dopant randomization is applied to it using three virtual widths, namely 1, 10 and 50  $\mu \text{m}$ , generating populations of 51 samples for each width (W is perpendicular to the figure). A region of 5 nm either end was left unperturbed to ensure good contact with the electrodes. In figure 2.4 examples of resulting

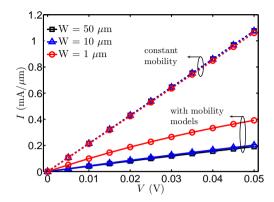

Figure 2.5: Median currents resulting from a simulation of 51 randomized resistors applying different virtual width (W). Mobility models are very sensitive to large doping concentration variations. W = 10  $\mu$ m represents a good choice for this doping level.

resistors are shown for W = 1  $\mu$ m and 10  $\mu$ m. As expected, the resistor with W = 1  $\mu$ m shows many 'zeros', red regions, while the resistor with 10- $\mu$ m width appears quite smooth (a very similar picture is obtained using 50- $\mu$ m width). Two sets of standard I-V simulations are performed: one was done applying a constant mobility and one using a doping dependent mobility model. The mobility model used in this experiment is the Philips Unified Mobility [48] model for the doping dependency (PhuMob in SD). The medians of the simulated I-V curves, scaled with W for quantitative comparison, are plotted in figure 2.5. In the case of constant mobility the value of the resistance changes only slightly from the obtained value for  $W = 1 \mu m$ . The value used for the constant mobility of the holes is  $\mu = 470.5 \text{ cm}^2/\text{Vs}$  which results in a resistance value for this piece of silicon of about 45  $\Omega$ . On the other hand, when the doping dependency mobility model is used the results are quite different. The effective resistance increases substaintially, whereas the resistor with  $W = 1 \mu m$  shows a much lower resistance (basically half) compared to the other widths. In fact, a resistivity value for this doping of  $0.0145 \Omega \cdot \text{cm}$  as calculated with this online tool [49] yields a resistance of about 250  $\Omega$ , very close to the value obtained with the resistor with larger width. The areas with low doping will create paths with "faster" holes that grossly affect the overall current.

In conclusion, if one wants to use a drift-diffusion simulator and obtain reliable results across the full bias range employing its mobility models, abrupt variations (exaggerated values) of doping concentration should be avoided.

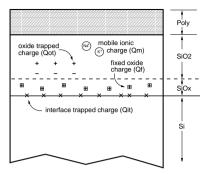

Figure 2.6: Terminology for charges associated with thermally oxidized silicon. After Deal [50].

Therefore, it was decided to always use a virtual width of at least 10  $\mu$ m in our simulations to assure a reasonable number of dopants at each grid point. This limits the approach discussed in this thesis in using a fixed width. This implies however, that when comparing simulations and measurements, the simulation results are scaled with  $\sqrt{W}$ . The drawback of this approach, also inherent to the use of a 2-D simulator, is the fact that it will not be able to capture narrow width effects and it will only be suitable for bulk MOSFET type of device architectures. As indicated in the introduction, this approach is in line with the more analogue and mixed-signal product strategy of NXP. In the following chapters, through the actual results, limitations of this approach will be investigated in more detail.

### 2.2.2 Random Interface state Fluctuation

A possible source of mismatch that can heavily affect the transistor behavior is the fluctuation of interface states. This was already introduced by Brews in 1972 [51]. The term interface-states is here used to indicate all the charges trapped at the interface between silicon and gate oxide ( $Q_{it}$  in figure 2.6). Fixed oxide charges, positioned in the bulk of the oxide, have not been considered in the simulations because, as shown by Putra et al. [52], they will not contribute significantly to mismatch. The main difference between fixed oxide traps and interface states is that the interface states, in the energy domain, occupy different levels in the band-gap: their charging state is thus dependent on the gate bias. Also, when the traps added to the device in the simulator are all with the same energy they will be filled (or emptied) all at the same gate

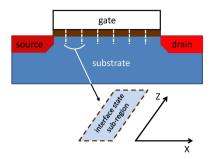

Figure 2.7: Schematic representation of a cross-section of a MOSFET and the implementation of interface states in it. The interface states are added to sub-regions in the oxide-silicon interface.

bias, dramatically reducing their impact on the variability. For a correct representation of this physical phenomenon, traps must be randomized in terms of concentration, energy and position along the interface [43]. The results of the investigation of the impact of interface state fluctuations will be discussed in depth in chapter 3.

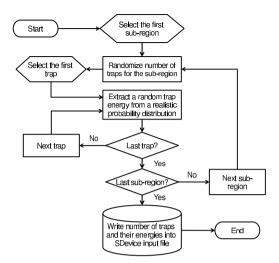

The general approach for the implementation of interface state fluctuation in SiSPET can be described as follows. The interface between silicon and gate oxide is divided into sub-regions each 2-nm long covering the entire gate length (see figure 2.7). An energy value (E) is selected from the band-gap using a uniform probability density function. The nominal concentration (and therefore the number N obtained multiplying the concentration with the virtual width) is calculated from an empirical equation that mimics a realistic parabolic shape, e.g.,  $N=60 \cdot E^2+40$  corresponding to a  $2 \cdot 10^{-11} {\rm cm}^{-2}$  at midgap to  $3.5 \cdot 10^{-11} {\rm cm}^{-2}$  at E=0.7 eV. The parabolic shape is based on a realistic trapsenergy distribution, as for instance reported in [53]. The acquired number of interface states is then randomized using a Poisson pseudo-random number generator, converted into density and assigned to the sub-region. This process is independently repeated until random interface states have been assigned to all the sub-regions along the channel.

#### 2.2.3 Random Series Resistance

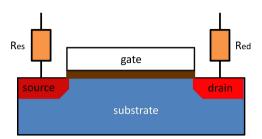

A final cause of mismatch that has been implemented and tested in SiSPET is indicated as random series resistance fluctuation. Recently, series resistance fluctuations have been studied in case of advanced device architectures such as FinFET, where the access resistance of the source and drain terminals heavily

Figure 2.8: Schematic representation of the device structure including the external series resistance added to drain and source terminals.

impacted the mismatch behavior [54, 55]. A similar effect can be observed in bulk MOS or, actually, in any other active device, when the whole deviceinterconnection system is affected by external (to the device) resistance fluctuations. In case of mismatch measurements, for instance, the external resistance can come from deteriorated probe-to-pad contact while in case of circuits they can come from asymmetric interconnections. In other words, the addition of series resistance fluctuations is meant to verify the influence of external perturbation to the system as a whole. The implementation of RSR in SiSPET is quite straightforward. Two lumped resistors of random value are added in the electrode definition (of source and drain) of the simulator. In figure 2.8 an idealization of the simulated device is depicted. Series resistors are added to source and drain terminals, their values,  $R_{\rm es}$  and  $R_{\rm ed}$ , are independently and randomly extracted from a uniform probability density function. The uniform distribution has been chosen especially to mimic the behavior of probe-to-pad resistance fluctuations during automatic probed measurements. To substantiate this choice some measurements have been performed. A schematic of the measurement test structure is shown in figure 2.9. It is a structure with a series of short-circuited pads, it is usually used to check if a probe card has been installed and landed on the wafer correctly. For this particular experiment four needles were used: the internal ones (2 and 3 in figure 2.9) are used to force a current into the pads, while all four needles are used to sense a voltage. Since the voltages at needles 1 and 4 are measured 'currentless' the probe-to-pad resistances are obtained with the equations:

$$R_2 = -\frac{V_{\rm SH} - V_{\rm H}}{I_{\rm F}} \tag{2.2}$$

$$R_3 = -\frac{V_{\rm SL} - V_{\rm L}}{I_{\rm F}} \tag{2.3}$$

Figure 2.9: Schematic of the test structure for probe-to-pad resistance measurements.

where  $R_2$  ( $R_3$ ) is the probe-to-pad resistance of needle 2 (3),  $I_F$  is the forced current and  $V_{\rm SH}$  and  $V_{\rm H}$  ( $V_{\rm SL}$  and  $V_{\rm L}$ ) are the voltages measured at needles 1 and 2 (4 and 3) respectively. These measurements have been performed on 180 positions on a 200-mm wafer with a semi-automatic wafer prober. This is exactly the same procedure as employed for standard mismatch measurements. Some typical results are shown in figure 2.10. In particular, two different behaviors have been selected as examples of what can be considered a 'good' and a 'poor' contact. In case of a good contact the distribution looks gaussian and also all the measured resistances form a narrow distribution. On the other hand, when a probe-to-pad contact shows a high resistance (this happened especially after the pads were deteriorated with multiple landings) the distribution is far from being Gaussian. The resistance varies substantially from 0.4 up to  $2.5 \Omega$ . A uniform distribution was chosen for the implementation of RSR in the simulator. In this case a log-normal distribution would have probably done the job as well. The point is however, that there is no reliable estimate for contact resistance in our type of experiments. It varies from experiment to experiment and it depends on pad contamination, sharpness of the needles, aluminum residues sticking to the needles and so on. A uniform probability density function has the advantages to be easy to implement, it will avoid negative numbers but it will overestimate the long tail of the 'poor' contact. RSR was added to the simulations only when the original measurements showed some unexpected results imputable to large probe-to-pad resistance fluctuations (see chapter 4). The range of the uniform distribution is fitted to drain current mismatch measurements. Note that, as it is for RIF also for RSR the aim is to study and understand the qualitative effect rather than using it as a method to extract quantitative information.

Figure 2.10: Distribution of probe-to-pad resistances measured on 180 different positions. Especially in case of high resistance value ('poor' contact), the distribution is non-gaussian.

### 2.3 TCAD calibration

Beside the choice and the implementation of these sources of mismatch, a crucial factor for the understanding of the mismatch behavior is the availability of a virtual virgin (unperturbed) device that resembles in the best possible way the actual measured device. A modern MOSFET consists of a quite complex architecture and doping profile. Good confidence in results from device simulations can be attained only when the virtual device is a "fair" copy of the ones actually fabricated<sup>1</sup>. This is a crucial step especially if the goal of the simulations is a better understanding of the mismatch dynamics in contemporary technology nodes. In general, the process of recreating the actual device with TCAD tools is called TCAD calibration. Basically, it consists of tuning device construction (either adjusting parameters in a process simulator or in a structure editor) and simulation model parameters until an acceptable level of agreement between simulated and measured electrical performance is reached for all the geometries and bias conditions under test. This task becomes particularly challenging when the device is drawn from scratch, even when the architecture is based on common scaling principles and inputs from the ITRS roadmap [56]. Quite often, detailed process parameters are unknown as they are considered trade secrets. This is for instance the case when the silicon is obtained from external foundries. In this section methodologies and

<sup>&</sup>lt;sup>1</sup>Of course, the target here is to obtain a very close resemblance to the **median** of a population of measured devices.

Figure 2.11: Representation of the indicators used for the TCAD calibration on the two drain current curves. The solid and dashed curves represent the drain current obtained with low and high drain voltage respectively.

techniques for such "blind" calibrations are discussed. Furthermore, due to the complicated doping profile that are typical for contemporary MOSFETs (and all the degrees of freedom of a simulator), targeting only parameters such as maximum current delivered,  $I_{ON}$ , threshold voltage,  $V_{T}$ , leakage current,  $I_{OFF}$ , drain induced barrier lowering, DIBL, and subthreshold slope, SS, as it is usually done, might not be sufficient. In fact, such a calibration can result in good agreement even with a doping profile far from the reality. This is an undesired situation because second order effects and peculiar mismatch behavior, for which TCAD is such a powerful investigation tool, may not be captured properly. An excellent way to verify the simulated device's doping profile is to evaluate the device behavior as a function of the substrate bias. The presence of halos (high tilt implants to improve short-channel behavior) for instance, makes the doping below the gate non-uniform in the lateral direction. When a substrate bias is applied, the depletion region below the gate will change. Thus, if the doping profile is wrong, it will have a different impact on the threshold voltage compared to measurements.

As explained, the device structure is created directly with SSE. Once the structure has been created (based on ITRS roadmap guidelines [56]) and the initial simulation performed, a comparison with measurements takes place. The classical and simple method consists of comparing the simulations with the measured current in the linear region (low drain voltage) and in the saturation regime (high drain voltage) first for long devices and then going down to the minimum dimensions [57]. The main performance indicators of MOS devices,

such as  $I_{\rm ON}$ ,  $I_{\rm OFF}$ ,  $V_{\rm T}$ , DIBL and SS, can be determined using these two curves as shown in figure 2.11. Once the measurement data have been collected, the real calibration begins. The simulator and the structure editor offer many adjustable variables and tunable parameters. Some of the main variables are:

- Doping profiles are obviously the most important device construction elements, as they play a role in any region of the device characteristic. In modern technologies, due to the presence of halos and composite well implant, there are many degrees of freedom (e.g., concentration and decay gradient).

- Oxide thickness and its dielectric constant predominantly affect the subthreshold slope and the current factor. The exact values of the thickness and the dielectric constant are often unknown. In modern technology the dielectric is slightly nitrided to reduce leakage and to increase the relative dielectric constant  $\epsilon_r$ .

- Drain and source **extension overlaps** determine how far drain and source extend beneath the gate and hence determine the *DIBL* and the actual current factor.

- Gate work function adjustments are used to shift the curve in one or the other direction to get the correct threshold voltage.

- Mobility model parameters play an essential role in determining the current in strong inversion.

Of these five "knobs", the mobility model requires a more detailed discussion. In most of the commercial device simulators there is a wide range of mobility models to choose from. The total effective mobility is the result of a combination of different physical effects, i.e. the mobility reduction due to high doping, degradation at interface due to electric field perpendicular to the carrier direction or the velocity saturation. Moreover, for each effect there are different formulations originating from different studies and approaches. Once the effects that need to be taken into account are selected, the user must choose from the different formulations. Finally, the simulator calculates the overall mobility by adding the different mobility effects following Mathiessen's rule [36]:

$$\frac{1}{\mu_{\text{tot}}} = \frac{1}{\mu_1} + \frac{1}{\mu_2} + \cdots \tag{2.4}$$

where  $\mu_{tot}$  is the total mobility and  $\mu_{1, 2}$  ... are the different mobility effects that are taken into account. In general, through modifying different sub-models of

the overall mobility, the user can affect the current under a particular bias condition while having a negligible effect on the others. For example the high field saturation model will mainly affect the current for high drain bias while the mobility degradation at the interface model will predominantly affect the current at low drain bias in long devices. Obviously, all parameters and variables must be kept identical for all the dimensions that will be considered during the analysis. The mobility models used for the simulations reported in this thesis are the Philips Unified Mobility [48] model for the doping dependency (PhuMob in SD), the mobility degradation at interface in the formulation proposed in [58] (Enormal in SD) and a high field saturation model as formulated in [59] (HighFieldSaturation in SD). The fitting parameters of these models were adjusted to match the measured currents. Furthermore, given the small dimensions of the transistor (60-nm gate length) a quantization model for the correct calculation of the carrier distribution was needed. The modified local density approximation (MLDA in SD) was chosen as quantization model because of its speed and computational robustness [60].

# 2.3.1 Example of experimental setup and calibration procedure

The technology that needs to be reproduced in simulations, for this calibration example, is a 65-nm Low Power bulk CMOS processed by TSMC [61]. The reference for the calibration was based on the median I-V characteristics of populations of 119 standard  $V_{\rm T}$  N-type MOSFETs measured over a 300-mm wafer at 25 °C. Two gate lengths are used for the calibration, namely  $L=1~\mu{\rm m}$  and 0.06  $\mu{\rm m}$  with fixed width  $W=1~\mu{\rm m}$ .